如何理解人工智能浪潮下的封装新逻辑?--晶通科技CTO即将带来深度解析!

9月18日,第四届功率半导体与先进封装测试创新高峰论坛将在无锡召开。作为功率半导体与先进封装领域的重要交流平台,本次论坛将聚焦先进封装、测试工艺与产业化挑战,吸引了来自产业链上下游的核心企业、科研机构与技术专家。

为了更好促进功率半导体和先进封装测试领域的相互交流与合作,半导体在线将于2025年9月18日在无锡市组织召开第四届功率半导体与先进封装测试创新高峰论坛,旨在提供协同创新的高质量交流平台,推动国内功率半导体及先进封装测试领域的学术研究、技术进步和产业发展。

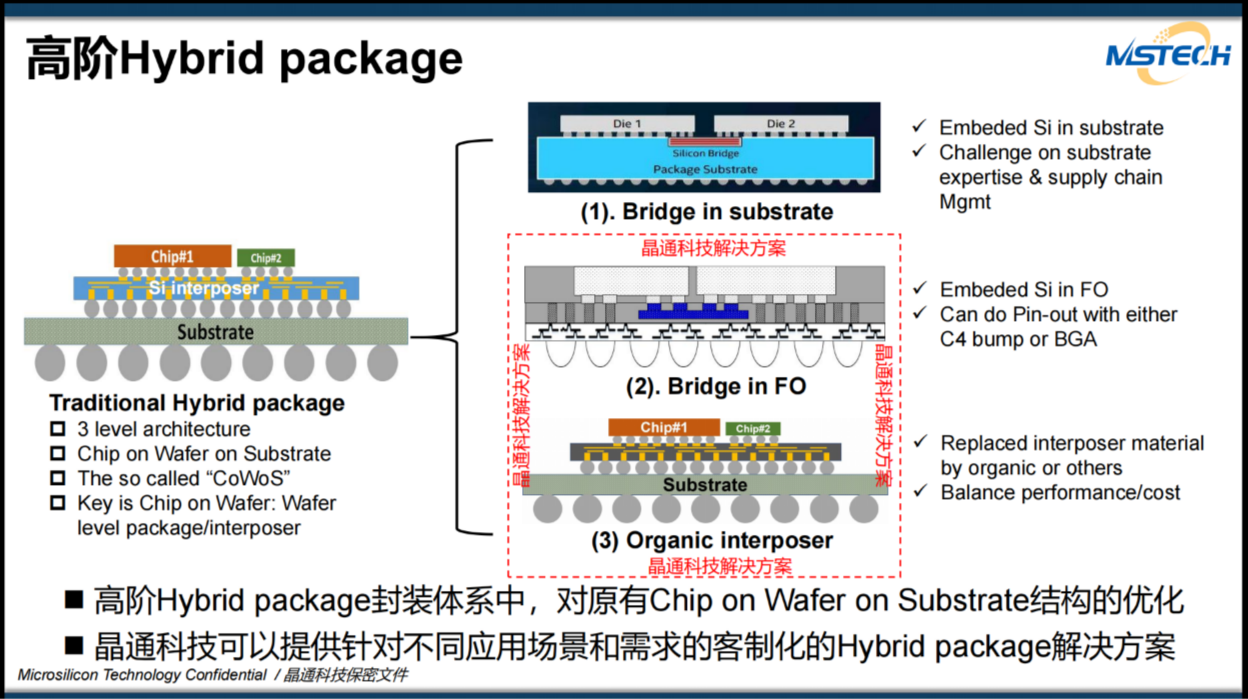

晶通科技首席技术官、联合创始人王新将作为受邀嘉宾,带来题为《混合封装Hybrid Package 的技术特点与工艺挑战》 的主题演讲。

混合封装 · 芯片设计进入“协同时代”

NEW TIME

当前,人工智能、大模型、高性能计算等应用的快速增长,正在推动芯片设计加速采用 Chiplet(芯粒化)模式。在这种模式下,如何高效、低成本地实现 2.5D/3D 集成,成为产业共同面临的挑战。

王新在即将到来的论坛中,将重点分享他对混合封装Hybrid Package 的理解与实践:

01.趋势 Trends

HPC/SoC 芯片正越来越多采用 Chiplet 模式,混合封装成为最具潜力的实现路径。

02.挑战 Challenge

Fan-out 与 Interposer 的技术融合,在良率、成本、可靠性等方面仍面临瓶颈。

03.方案 Solution

晶通科技提出的嵌入式硅桥扇出型混合封装,在架构设计、互联性能、工艺流程等方面展现出差异化优势。

王新认为:“未来的先进封装,必须打破工艺壁垒,走向设计、架构、材料、设备的多维度协同。混合封装不仅仅是技术路线的选择,而是系统竞争力的关键所在。”

论坛前瞻 · 值得关注的声音

PROSPECT

在先进封装正逐渐成为半导体产业“第二战场”的背景下,本次论坛的讨论将不仅涉及功率半导体与测试工艺的迭代,也将聚焦系统级创新如何落地。王新的分享,将为产业链上下游企业提供一个实践案例与思路参考:

• 如何理解Chiplet 浪潮下的封装新逻辑?

• 混合封装能否成为性能与成本平衡的最佳解?

• 晶通科技针对人工智能AI芯片的高阶封装方案

答案,将在9月18日的论坛现场揭晓。

演讲时间:2025年9月18日(周四)地 点:无锡苏宁银河国际酒店,无锡市梁溪区人民中路109号

标签: